在将晶圆制成半导体的过程中需要采用数百项工程。其中,一项最重要的工艺是蚀刻(Etch)——即,在晶圆上刻画精细电路图案。蚀刻(Etch)工程的成功取决于在设定的分布范围内对各种变量进行管理,并且每一台刻蚀设备都需做好在最佳条件下运行的准备。我们的刻蚀工艺工程师运用精湛的制造技术,完成这一细节工艺的处理。

SK海力士新闻中心对利川DRAM Front Etch(蚀刻)Middle Etch以及End Etch技术团队成员进行了访谈,以此来进一步了解他们的工作。

蚀刻(Etch):生产率提升之旅

在半导体制造业中,蚀刻(Etch)指在薄膜上雕刻图案。图案使用等离子体喷涂而成,形成每个工艺步骤的最终轮廓。它的主要目的是根据布局完美呈现精确图案,在任何条件下都保持统一一致的结果。

如果沉积或光刻(Photolithography)工程中出现问题,可通过选择性蚀刻(Etch)技术解决问题。但是,如果蚀刻(Etch)工程过程中出现问题,则情况无法逆转。这是因为无法在雕刻区域填充相同材料。因此,在半导体制造过程中,刻蚀对于确定总体良品率和产品质量至关重要。

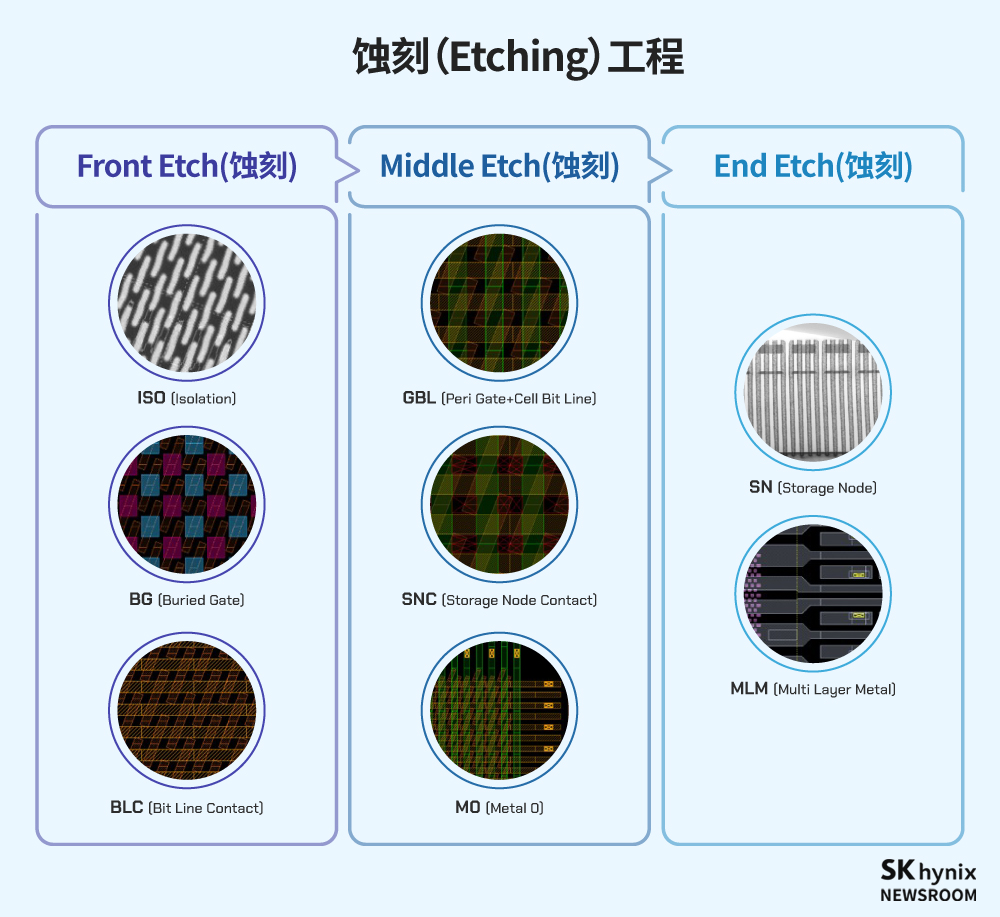

刻蚀工艺包括八个步骤:ISO、BG、BLC、GBL、SNC、M0、SN和MLM。

首先,ISO(Isolation)阶段进行晶圆上的硅(Si)蚀刻(Etch),创建有源单元区。BG(Buried Gate)阶段形成行地址线路(Word Line)1和栅极,打造电子通道。接下来,BLC(Bit Line Contact)阶段会在单元区内创建ISO与列地址线路(Bit Line)2之间的连接。GBL(Peri Gate+Cell Bit Line) 阶段将同时创建单元列地址线路与外围3中的栅极。

SNC(Storage Node Contract)阶段继续创建有源区域和存储节点4之间的连接。随后,M0(Metal0)阶段形成外围S/D(Storage Node)5的连接点以及列地址线路与存储节点之间的连接点。SN(存储节点)阶段确认单元容量,之后的MLM(Multi Layer Metal)阶段创建外部电源和内部布线,整个蚀刻(Etch)工程过程随之完成。

鉴于蚀刻(Etch)技术人员主要负责半导体的图案化工作,因此DRAM部门被细分为三个团队:Front Etch(蚀刻)(ISO、BG、BLC);Middle Etch(蚀刻)(GBL、SNC、M0);End Etch(蚀刻)(SN、MLM)。这些团队也会按照制造岗位和设备岗位划分。

制造岗位负责管理和改进单元生产工艺。制造岗位通过变量控制和其他生产优化措施来提高良品率和改善产品质量,因而具有十分重要的地位。

设备岗位负责管理和强化生产设备,以便规避刻蚀工艺过程中可能出现的问题。设备岗位的核心职责是确保设备的最佳性能。

虽然职责分明,但所有团队均朝向共同的目标而努力——即,管理和改进生产工艺及相关设备,进而提高生产率。为此,各团队积极分享各自的成果以及亟待改善的领域,通过合作提高业务表现。

如何应对小型化技术挑战

SK海力士于2021年7月开始量产适用10nm(1a)级工艺的8Gb LPDDR4 DRAM产品

半导体存储器电路图案已经进入10nm时代,并且经过改进后,单个DRAM中可容纳约1万个单元。因此,即使在刻蚀过程中,工艺裕度也会有所不足。

如果形成的空穴(Hole)6过小,可能会出现“未打开”状态,从而阻塞芯片下端部分。此外,如果形成的空穴过大,可能会出现“桥接”现象。当两个空穴之间的间隙不足时,就会出现“桥接”现象,导致后续步骤中出现相互粘接问题。随着半导体日益精细化,空穴的尺寸数值范围正在逐渐缩小,这些风险也将逐步消除。

为了解决上述问题,刻蚀技术专家们不断改进工艺,包括修改工艺配方和APC7算法,以及引入ADCC8和LSR9等全新刻蚀技术。

随着客户需求愈发多样化,另一个挑战随之出现——多产品生产趋势。为满足客户的此类需求,每种产品的优化工艺条件需要单独设定。对于工程师们来说,这是一项非常特殊的挑战,因为他们需要让量产技术同时满足既定条件和多元化条件的需求。

为此, Etch(蚀刻)工程师们引入了“APC offset”10技术来管理基于核心产品(Core Product)的各种衍生品,同时建立并利用“T-index系统”来综合管理各项产品。通过这些努力,系统得到持续改进,得以满足多产品生产需求。

我们一起听一听蚀刻 (Etch)工程工程师们的心声

能否介绍一下在工作中需要哪些技能?

金何那,技术负责人(TL)

我的职责是根据生产工程师的测量数据,评估改善分散性、提高良品率以及提升生产率的效果。由于蚀刻(Etch)工程涉及通过各种联动工艺制成的Hard-mask11,因此需要进行细致而准确的分析。最终的图案必须在刻蚀过程中敲定,因此我们必须要在联动工艺发生变化时迅速作出响应。准确分析与全面了解半导体生产相关的数据是形成最终完整图案的关键。

柳太熙 TL

作为设备工程师,我负责设备的维护、修理、设置和拆卸等工作。设备工程师最重要的工作是维护设备,确保生产能够在最佳条件下进行。如果机器能始终如一地运行,那就再好不过了,但事实上,机器状态会随着各种变量而不断发生变化。因此,设备工程师需要拥有广阔的视角,能够从多个角度评估各种问题。

你们如何持续拓展自己的技术专长?

金珉湖 TL

紧跟最新技术发展趋势,这一点非常重要,当然现在来看,数据使用也很重要。我们需要弄清数据点之间的相互关系,比如生产过程中生成的设备数据与作为结果显示的响应数据之间的关联。因此,我正在学习统计理论,以便在分析中使用。

李在镛 TL

考虑到技术类制造工作的性质,我们必须首先确保生产的稳定性。因此,我会仔细检查各个方面。由于工艺技术和设备技术是相互兼容的,所以我们不仅要了解生产工艺,还要对设备有全面的了解。因此,我在业余时间不断学习设备相关知识。我们的团队提供在工艺和设备岗位之间轮换的机会,旨在帮助成员提升这两个学科的知识。

您认为您的工作带来了什么样的回报?

金何那 TL

通过改变生产条件来提高产品良率,这是非常有意义的事情。刻蚀是与产品良率休戚相关的一个核心步骤,这一点让我倍感自豪。但与此同时,想到即使是一个小小的错误也会对产品良率造成重大影响,我有时也会倍感压力。所以,每当我安全地将优质晶圆移交至下一步生产工序时,我都会有一种成就感。

李在镛 TL

刻蚀工艺有时被称为半导体生产的顶峰,因为它通常决定着产品良率。因此,成功解决每一项任务与我而言都有着特殊的意义。这就是这项工作的魅力所在,当我突破困难、解决各种问题时,我会感到有成就感。而通过分享工艺改进知识来积极影响其他同事,同样让我感到无比自豪。

你们的团队及整个部门的氛围怎么样?

柳太熙 TL

我们都为能成为团队一员而感到无比自豪,因为蚀刻(Etch)是一项十分复杂的工艺技术,在整个半导体制造过程中有着举足轻重的作用。所有团队成员都全身心地投入到自己的工作中,形成一股充满活力、积极向上的工作氛围。这种积极的工作氛围还源于团队成员对私人时间的重视——因此我们能够很好地平衡工作和生活。

金珉湖 TL

我们拥有横向平等的企业文化,每个人都可以踊跃表达自己的意见。当然,涉及到工作时,我们会严肃以待,我们有着合作互助、彼此尊重的团队氛围。晶圆厂需要7天24小时不间断运转,因此我们的工作范围也十分的广泛。这意味着有时我们可能需要将工作与生活之间的平衡放在次要位置。但是作为一个团队,我们真诚地尊重彼此,并且注重良好沟通,因此我们会加倍努力,来帮助彼此保持良好的平衡。

1Word Line:与晶体管源极部分连接的线路,负责读取和写入。

2Bit Line:穿过晶体栅极的线路。当在线路上施加高于特定水平的电压时,晶体管将导通并做好数据读取或写入准备。

3Peri:控制单元运行的外围电路。

4Storage Node:管理DRAM中数据存储的扇区,特别是数据存储介质的下电极。

5S/D (Source/Drain):源极发射电子,漏极接收电子。

6空穴: 价带中电子运动产生的空电子层。

7APC(Advanced Process Control):根据设定的计算值自动调整每个生产变量的程序。

8ADCC(Active DC Control):通过调整直流控制器来控制由射频时间决定的相互关系的功能。

9LSR(Lam Spectral Reflectometer):一种根据晶圆中心的光反射角来计算和估算刻蚀深度,以此调整刻蚀量的方法。

10APC Offset:根据各项产品的响应性能,以某个产品(通常是核心产品)为核心,按照特定标准追踪变量的自动化程序。

11Hard-mask:在沉积光刻胶阶段之前使用的、具有高刻蚀选择性的材料,因为光刻胶单独提供的余量不足,很难完全芯片下端部分的刻蚀。