被称为 “有史以来最大的典范转移(Paradigm Shift)”的人工智能(AI,Artificial Intelligence)正在以惊人的速度走入我们生活的中心。不论是自动驾驶汽车、人工智能助手还是模仿人脑的神经形态半导体,人工智能的智力和学习速度已超越人类,并正通过学习人类生活的方方面面将其应用扩展到各个领域。那么,人工智能技术有哪些主要应用,又是如何实现这些应用的呢?

(点击查看首尔大学郑德均教授关于AI半导体的更多见解!)

云计算 vs. 边缘计算

图1:云计算 vs. 边缘计算

作为一种人工智能应用,边缘计算1与云服务互为反面。视频和图像等需要处理大量输入数据的应用必须使用边缘计算处理数据,或通过有线/无线通信将尽量少量的数据传输到云服务。因此,专为边缘计算设计的加速器占据了AI芯片设计的很大一部分。用于自动驾驶领域的AI芯片就是很好的例子:这些芯片利用卷积神经网络2 (CNN,Convolutional Neural Network)和一系列神经运算来处理含有大量数据的图像,从而进行图像分类和物体检测。

AI和隐私问题

人工智能应用的另一领域是对话式服务,例如亚马逊的Alexa或SK电讯的NUGU等智能音箱设备。然而,如果用户隐私得不到保护,这种服务就不能被广泛使用。若此类设备持续通过麦克风窃听用户在家中的对话,对话式人工智能服务便难以超越简单娱乐服务的本质进行进一步开发。因此,许多企业正致力于为此类隐私问题寻找更好的解决方案。

解决隐私问题的最新研究趋势是同态加密3。同态加密不会原封不动地传输用户语音或医疗数据等敏感信息。在无需提前解密的情况下,这种加密形式能在云服务上以密码文本的形式处理只有用户能解密的加密数据,对它们进行所需的计算。在同态加密中,计算后的结果以加密形式再次发送给用户,只有他们能解密查看。因此,除了个人用户之外,包括服务器在内的任何一方都无法看到原始数据

包括服务器在内的任何一方都无法看到原始数据。同态服务与一般的明文深度神经网络4(DNN,Deep Neural Network)服务相比,需要高达几千或几万倍的巨大计算量。未来研究的关键领域将围绕如何通过专门设计的同态加速器5大幅提高计算性能,进而缩短服务时间。

AI芯片和存储器

在大规模的深度神经网络中,单个处理器中无法包含如此大量的所有权重。因此,当需要处理存储于外部大容量DRAM中的权重时,必须进行读取访问,并将外部权重带到处理器中。如果这些权重只被使用一次,且在单次访问后不能重复使用,那么从外部拉取数据的过程将浪费不少能量和时间。这是一个极其低效的方法,因为与在处理器中存储和利用所有权重的方法相比,这种方法产生了额外的时间和能量消耗。因此,要在大规模的深度神经网络中使用大量的权重来处理大量的数据,需要并行连接和/或多次使用相同权重的批量操作。换句话说,需要通过将几个处理器与DRAM并行连接来进行计算,将权重或中间数据分散存储在几个DRAM中,以便重复使用。在这种结构中,处理器之间的高速连接是必不可少的,与让所有处理器通过一条路线访问相比,它的效率更高。而且,只有这种结构可以提供最高的性能。

AI芯片的互连互通

图3:AI芯片的互连网络

连接众多处理器时的性能瓶颈取决于带宽、延迟以及互连形式。这些因素决定了深度神经网络的规模和性能。换句话说,如果企图通过并行连接N个加速器来使性能提升N倍,互连的延迟和带宽会导致瓶颈的出现,期望的性能提升幅度也无法实现。

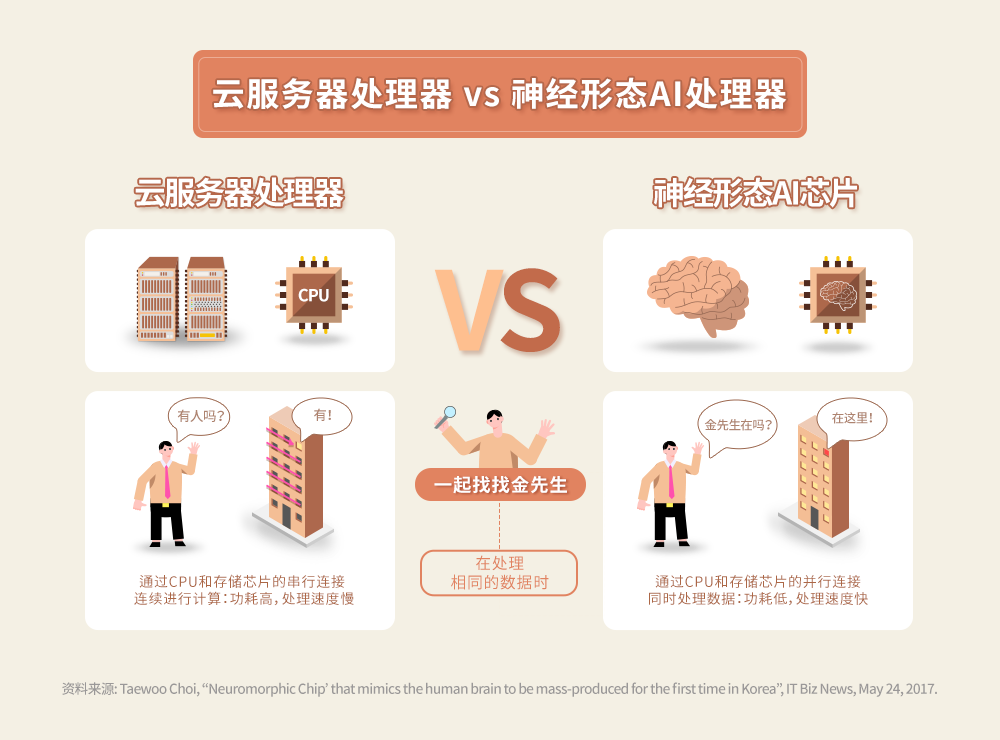

因此,处理器和处理器之间的互连结构对于性能的可扩展性而言至关重要。对英伟达的A100 GPU而言,NVLink 3.0便发挥了这一作用。这款GPU(图形处理器,Graphics Processing Unit)有12个NVLink通道,每个通道提供50GBps的带宽。4个GPU间各用4条通道连接在一起,构成团结构。但要连接16个GPU,则需要专用于互连的外部芯片NVSwitch。而谷歌TPU v2则被设计成能够使用核间互连(ICI,Inter-Core Interconnect)连接一个二维环面结构,总带宽为496 GBps。

图4:使用6个HBM的英伟达GPU加速器A100

(资料来源: The Verge)

处理器的互连方式对整个系统有巨大影响。例如,如果以网状(mesh)或环状(torus)结构互连,由于芯片间的物理连接很简单,组成这样的结构便很容易。但由于距离较远的节点间互连需要跳过几个处理器,其延迟与距离便成正比增加。最极端的方法是将所有处理器一对一地互连起来,形成团(clique)结构,但这将导致芯片引脚(pin)数量的大幅阶乘增加,使印刷电路板的拥挤程度超出允许范围。因此,在实际设计中,这种方法最多只能连接四个处理器。

在多数情况下,使用像NVSwitch这样的交换开关是另一个有吸引力的选择,但这种方法也将所有连接集中在交换开关上。因此,由于传输线集中在交换开关周围,互连的处理器数量越多,印刷电路板布局就越困难。最好的方法是将整个网络架构成二叉树(binary tree),在底端连接处理器,并将最大带宽分配给二叉树的顶端。因此,创建胖树结构(binary fat tree)将是最理想的,这种结构能够提供最大的性能与可扩展性。

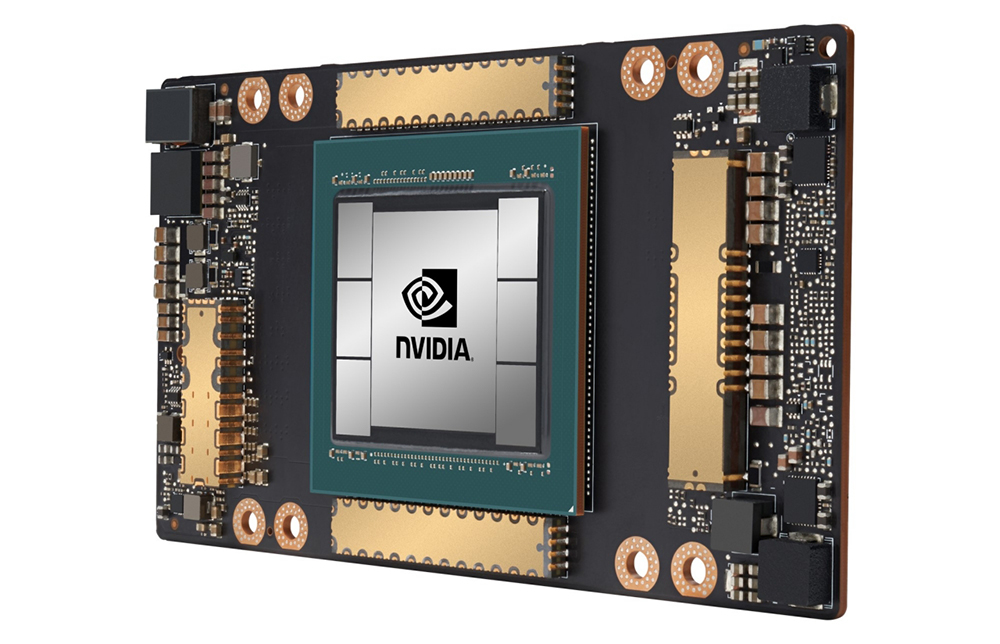

神经形态AI芯片

图5:云服务器处理器 vs 神经形态AI处理器

作为深度神经网络加速器的云服务器所使用的处理器在数据表示和处理方法上,都采取数字形式,其计算结构从根本上看,是在硬件之上通过软件模拟神经网络。最近,有越来越多关于神经形态AI芯片的研究一改以往的模拟方法,直接模仿生物体的神经网络及其信号,将其映射到模拟电子电路上,并以同样的方式处理信号。这种方法对实际应用中的原始数据表示采取了模拟的形式。这意味着一个信号在一个结点中表示,且相互连接是由硬线(hardwire)而非由软件实现,权重则是以模拟形式存储的。

图6:现存半导体 vs. 神经形态半导体

这种结构的优点在于它具有最大的并行性,且同时可以用最少的能量运作。神经形态芯片在某些应用中可以提供很大的优势。由于结构是固定的,它缺乏可编程性,但在某些小规模的边缘计算应用中可以有很大优势。事实上,神经形态处理器在处理物联网中传感器的人工智能信号等应用中具有重要意义,它可以提供高能效,也能进行需要使用固定权重卷积神经网络处理大量视频数据的图像分类任务。然而,由于权重是固定的,它很难用于需要持续学习的应用领域。另外,出于在大规模计算时的结构限制,它很难利用将几个芯片并行互连的并行性,导致其实际应用范围仅限于边缘计算。我们也有可能以数字形式实现神经形态的结构,IBM的TrueNorth芯片就是一个例子。然而我们也知道其可扩展性是有限的,这使得它很难找到广泛的实际应用。

AI芯片的发展现状

为了创造能与人类对话的智能数字助理,需要处理大量用户数据的Meta公司(原Facebook)正在设计一款专用于掌握关于世界的基本知识的AI芯片。除此之外,Meta内部还正开发用于审核内容并决定上传至Facebook的实时视频能否被发布的AI芯片。

专注于电子商务和云计算的技术公司亚马逊,现已开发了自家的人工智能加速器AWS Inferentia,为其数字助理Alexa助力,并利用它来识别音频信号。云服务提供商AWS已经开发了使用Inferentia芯片的基础设施,并为云服务用户提供像谷歌TPU一样可以加速深度学习工作负载的功能。

另一方面,微软在其数据中心使用现场可编程门阵列(FPGA,Field Programmable Gate Array),并引入了一种根据应用算法重新配置精度和深度神经网络结构以确保最佳性能的方法,以此打造在当前应用和未来应用皆有最优表现的AI芯片。然而,即使已经确定了最佳结构,为了重新配置结构和逻辑电路,这种方法仍然产生了大量的间接开销。与为某些目的特定设计的ASIC芯片相比,该方法在能耗和性能方面不可避免地处于劣势,因此,我们仍不清楚其实际效益。

当下,一些初创芯片设计公司(fabless)正在通过开发不专用于某些应用领域的通用可编程加速器,以此与英伟达竞争,包括Cerebras Systems、Graphcore和Groq在内的许多公司也纷纷加入这场激烈的角逐。在韩国,SK电讯与SK海力士合作开发了SAPEON,并即将以其作为AI芯片用于数据中心。与此同时,Furiosa AI也正准备将其AI芯片Warboy商业化。

图7:SAPEON X220

(资料来源: SK电讯新闻稿)

编译器的重要性

此类人工智能硬件的性能在很大程度上取决于其软件的优化程度。要通过收缩阵列同时操作数千或数万个计算电路并有效地收集结果,需要高度的协调。设置输入数据的顺序,使人工智能芯片中的众多计算电路连续工作,并将输出传输到下一阶段,这些任务只能通过专门的库(library)来完成。这意味着,开发高效的库以及使用库的编译器与设计硬件同样重要。

英伟达GPU在最初是一个图形引擎。但英伟达开创了名为CUDA的开发环境,使用户能够轻松地编写程序,并使其能够在GPU上高效运行,这让它在整个人工智能行业取得了高人气的普遍应用。谷歌也提供了自己的开发环境TensorFlow,以支持用户轻松利用TPU,帮助他们使用TPU开发软件。可见,未来我们需要更丰富、更多样化的开发环境,增加人工智能芯片的适用性。

AI芯片及其能源消耗

未来AI服务的方向绝对要以提高服务质量和降低所需能耗为重点。因此,预计在未来,人类将围绕降低AI芯片的功耗和加速开发节能的深度神经网络结构而努力。事实上,在ImageNet的训练中,需要10^19次浮点运算才能将错误率降低到5%以下,这相当于整个纽约市的居民一个月所消耗的能源量。以2016年AlphaGo与9段职业棋手李世石的围棋比赛为例,下围棋时的推理共使用了1202个CPU和176个GPU,预估耗电量为1兆瓦。与人脑仅使用20瓦相比,这是非常巨大的能量消耗。

后来开发的AlphaGo Zero只用4个TPU进行自我强化学习,却在区区72小时的训练后便取得了超过AlphaGo系统的表现。这个案例证明了使用全新的神经网络结构和学习方法来减少能源消耗的潜力。而我们必须继续对节能的深度神经网络结构进行研究和开发。

AI半导体市场的未来

图8:AI芯片的市场前景

(资料来源:Statista)

在AI领域取得的成就将扩大相关技术的应用范围,也将引发惊人的市场增长。例如,为解决AI和大数据处理中的数据访问瓶颈问题,SK海力士最近开发了下一代智能内存半导体PIM6(Processing-in-Memory,内存中处理)。SK海力士公布了“GDDR6-AiM(内存加速器)”样品,将其作为首个应用PIM的产品,更在2022年国际固态电路会议7(ISSCC,IEEE International Solid-State Circuits Conference)上宣布了PIM开发成果。ISSCC是在半导体领域具有最高权威的国际会议,已于今年2月底在旧金山举行。

图9:SK海力士开发的GDDR6-AiM

应用系统将进一步开创更宽阔的AI市场,不断创造新的领域,进而以基于神经网络结构的推理质量为支撑,实现更为出众的服务质量。作为AI系统的骨干,能以低能耗快速及准确地进行推理和训练任务的AI半导体亦将脱颖而出。最新的研究结果表明当前的能源效率本身是非常低的,因此,我们更需要研究新的神经网络结构,并同时关注功能和能源效率。而在硬件方面,定义能源效率的核心在于改进内存访问方法。因此,在内存中处理数据而无需单独访问的PIM技术,以及通过在模拟内存中存储突触权重来模仿神经网络的神经形态计算将成为重要的研究领域。

1边缘计算(Edge Computing)是一种分布式计算范式,它能够使计算和数据存储更接近于数据源。

2卷积神经网络(CNN,Convolutional neural network)是一种用于图像的识别和处理的人工神经网络,专门用于处理像素数据。

3同态加密(Homomorphic Encryption)是一种加密形式,允许用户在不解密的情况下对其加密的数据进行计算。

4深度神经网络(DNN,Deep Neural Network)是一种在输入和输出层之间有多层的人工神经网络。

5加速器(Accelerator)是一种利用处理和计算芯片制成的特殊用途硬件。

6内存中处理(PIM,Processing-in-Memory,亦称内存中处理器)为新一代技术。它通过在内存中增加计算功能,为AI和大数据的数据拥堵问题提供解决方案。基于这种技术的产品亦被称为PIM芯片。

7国际固态电路会议(ISSCC,IEEE International Solid-State Circuits Conference)已于今年2月20日至2月28日在线上举行,主题为“面向可持续世界的智能硅片(Intelligent Silicon for a Sustainable World)”。

郑德均博士

Professor

Electrical & Computer Engineering

Seoul National University(SNU) College of Engineering