存储芯片技术和业务的核心在于“存储密度扩展”。这意味着内在包含多个可以传输并保留信息的单元(bit) 。存储芯片需求方针对存储芯片的要求是各种各样的,包括速度和可靠性等,其中对存储空间的渴望最大。

您可能会认为,增加存储密度可以提升存储容量,因此半导体价格也会更加昂贵。但是存储芯片的价格与存储密度并不成正比。实际上,价格与存储密度无关甚至也会成反比,一般会在1到8美元范围内随时变动。从而导致全球约40家公司未能适应其变化被淘汰。最近十年的时间,生产DRAM和NAND的公司各只有三到四家幸存了下来,并其在全球市场上占有一席之地。

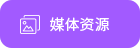

1. 存储芯片存储密度增加的规律为每十年增加约1000倍(210)

图1. DRAM与NAND存储密度增长趋势的年度比较

存储芯片的存储密度最初要从20世纪70年代的1Kbit DRAM开始算起,并呈现出每十年增加约1000倍(210)的趋势。20世纪80年代属于兆比特时代,20世纪90年代和21世纪则属于兆比特增长到千兆比特的时代。

然而,存储器实际存储密度的真正赢家是当属21世纪初出现的NAND。最初,在NAND发展初始阶段,市场上出现了容量为128Mbit(Mega:220)和256Mbit,小于1Gbit的SLC产品,经过十年的发展,容量为64Gbit(Giga:230)和128Gbit,跟之前相比增加约1000倍的MLC产品出现并成为主流。在本世纪20年代初,存储密度达到比Gbit 大 1000倍的 1太比特(240),即TLC产品开始成为主流产品。

这表明NAND的存储密度在每10至15年间增加了大约1000倍。在这种趋势下,预计在21世纪30年代初,存储密度是太比特1000倍的贝脱比特(250)(QLC-NAND)时代将会到来。一本书占用的内存不足10Mbit,一部电影占用的内存约为20Gbit。这意味着1Tbit可储存10万多本书,相当于一个人要花一辈子才能读完数量,或者储存数十部电影。

在DRAM方面,在2020年存储密度维持在NAND存储密度的1/100倍,容量为64Gbit至128Gbit的产品(DDR5)已于近期推出。随着时间的推移这一差距将会越来越扩大,预计到2030年将达到1000倍,到2040年将超过10000倍。

2. 存储密度最大化和芯片表面积最小化→主导价格

![]()

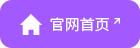

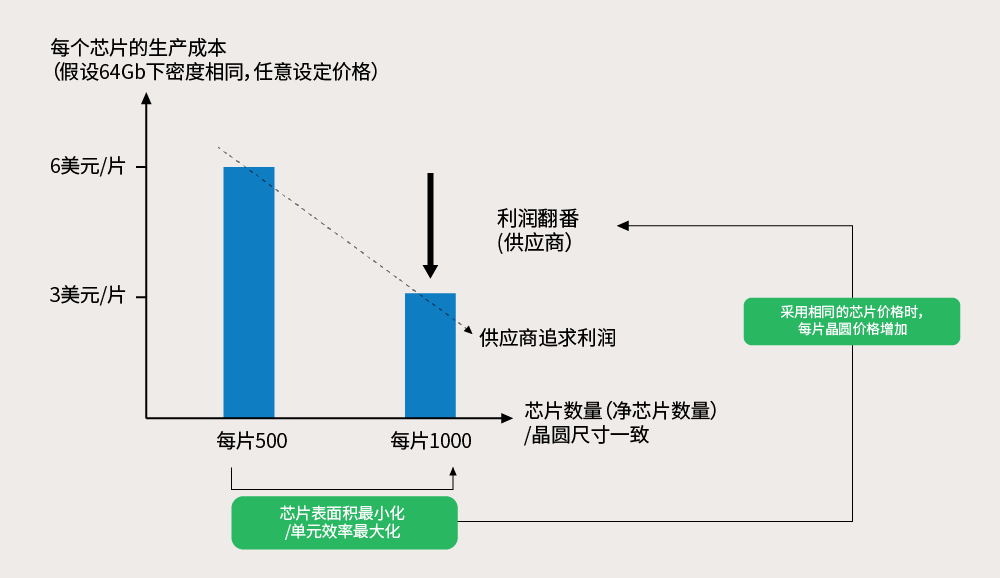

图2. 半导体定价结构

供应商致力于最大限度地增加每个芯片的存储密度或晶圆中芯片的数量,从而降低半导体的销售价格或单位成本。增加每个芯片存储密度的目的不仅是因为需要在芯片中存储尽可能多的数据,同时也是因为客户不断寻求降低半导体的成本。另一方面,之所以增加晶圆或净芯片中的芯片数量,是因为供应商不管市场需求如何都希望能够实现成本节约。换句话说,更高规格的存储密度符合供需双方的共同利益,而芯片或净芯片数量的增加纯粹有利于供应商提高利润。

在这方面,供应商增加每个芯片的存储密度和每个晶圆的净芯片数,旨在同时满足提高密度和节省成本这两方面的需求,同时又降低利润。这体现了半导体行业的“小鸡博弈”,即试图通过降低盈利能力、提高市场份额的策略来战胜市场上的竞争对手。在这种情况下,供应商必须创造一个使自身获得利润,同时使竞争对手遭受损失的环境。这只有在供应商的成本与其竞争对手的成本之间存在显着差距时才有可能。

在成本竞争中获胜的供应商能够在价格上获得主导地位。因此,供应商调动一切能力(包括技术和销售条件等),奉行低成本策略从而增加全球市场份额。如果这种情况持续下去,竞争对手将无法改善利润结构,不可避免地会被市场淘汰。例如,前全球DRAM半导体公司尔必达(Elpida Memory)和德国英飞凌公司(Infineon)便是在这样的“小鸡博弈”中败下阵来。他们要么出售DRAM业务,要么退出市场,即便国家层面上做出了许多努力来重振这些公司也无济于事。

2-1. 存储密度最大化→降低位元生产成本

图3. 在任意设定的芯片价格下,通过增加芯片存储密度来降低位元生产成本

一般而言,增加存储密度会涉及到新产品规划,基于设备技术进行的设计,以及对功能和可靠性进行相应的完善。要增加存储密度,就需要通过增加单元的数量,即便这样做会稍微增大芯片的尺寸,或是通过电子方法增加位元的数量。在半导体中,物理单元指的是晶体管(Transistor,TR)。所以,必须使晶体管更小或尽量缩短连接晶体管电路的宽度。这是采用传统方式缩小存储芯片的一些示例,适用于包括DRAM和NAND在内的所有存储器。

增加位元数的产品化方法与其他方法的不同在于,是根据一定尺寸的单元内电子存储容量水平的区分。它不是一种物理方法,因此与晶体管的大小或电路线宽无关。增加物理单元中的位元数只适用于NAND的选项之一。目前,主要的NAND产品可以在每个单元存储三位信息(三层单元,TLC)。DRAM产品每个单元可存储1位信息,必须通过物理方法降低每位的成本。然而NAND产品每单元可存储3位信息,可以同时使用物理方法和电子方法,因而更具优势。因此,存储密度发展的主导地位已经从DRAM转移到NAND。由于各种原因,就每个位元的成本而言,DRAM的成本是NAND的10倍以上。

当产品存储密度增加时,该产品的价格也会随之上涨。然而,价格的上涨幅度小于存储密度的增长幅度。因此,即使价格上涨1.5倍,存储密度最多会增加4倍(2~4倍)。也就是说,需求方可以获得2.5倍以上的收益。换句话说,即便新半导体产品价格高昂,存储密度的增加幅度会超过价格的上涨幅度,使其有利于需求方,同时通过降低每位的价格也为供应商创造有利结构。然而在现实中,存储密度的增加会使芯片尺寸和其他变量也随之增加。而与规划阶段不同的是,产品发布的价格可能会根据发布时间等市场变量而有所不同。

2-2. 芯片尺寸最小化→降低位元生产成本

图4. 在任意设定的芯片价格下,通过增加每个晶圆的芯片数量来降低每个芯片的成本

增加每个晶圆的芯片数量需要通过物理方法来尽量减少芯片的表面积。这需要缩小电路线宽或使单元效率达到最大来减小芯片尺寸。但是,缩小电路线宽会使器件(晶体管)的可靠性和功能受到影响。因为单元尺寸变小会有一些限制,所以需要通过设计规则寻找最佳设计条件来增加芯片的数量。

狭义的设计规则是指在保证设计电气特性的前提下,布置导线宽度和导线间物理空间的最佳条件。而从广义上讲,设计规则是指为工艺状态、封装的物理形式和允许的电气条件等各种因素建立最优条件。最大限度的增加每个芯片的数量可以提高每个芯片的价格,最终帮助供应商降低每个芯片的成本。

3. IDM公司的兴衰

图5. 全球DRAM IDM公司数量的年度变化(不包括在全球DRAM市场占有率低于3%的公司)

从1970年的英特尔开始,存储芯片业务被认为是一项利润丰厚的业务。随着20多家美国电子公司进入该行业,使其成为了以美国为主导的行业。到了上世纪80年代,以日立为首的约10家在日本的全球电子公司也进入市场,缔造了半导体行业的蓬勃发展。此后,半导体热蔓延到韩国,形成了三星电子、SK海力士(原现代电子)和LG半导体“三足鼎立”的态势。欧洲近10家ITC公司也将半导体视为极具获利前景的业务,其中包括SGS汤姆森微电子公司。因此,从上世纪70年代到90年代,全球大约有40家公司进入该市场。但由于成本争夺战,每十年就有大约10家公司消失。在经历两场激烈的“小鸡博弈”之后,那些曾经凭借非凡技术出类拔萃的杰出公司逐渐从市场上消失。目前,三家DRAM IDM公司(三星电子、SK海力士和美光)和四家NAND IDM公司(三星电子、SK海力士、铠侠(前东芝)和美光)正在巩固他们的地位和影响力。

除了今天介绍的提高存储密度和降低成本的方法外,还有其他几种选择。包括从2D向3D的演变措施,应用EUV和新的处理方法,增加每个单元的位元数(NAND)、TSV(DRAM)和4D等结构改进采用多方面的方法。PCRAM、MRAM、ReRAM等基于NAND概念的新产品有望成为下一代存储器。在对需求者有利的市场中,可能随时出现通过节约成本来平衡产品定价的策略。同时供应商也能够以挑战性环境为契机,大幅超越竞争对手。

陈锺文半导体专栏作家

韩国忠北半导体高等学校老师